| IF | ID | ΕX | MEM | WB  |     |     |     |    |

|----|----|----|-----|-----|-----|-----|-----|----|

| ļi | IF | ID | ΕX  | MEM | WB  |     |     |    |

| t  |    | IF | ID  | ΕX  | MEM | WB  |     |    |

|    |    |    | IF  | ID  | ΕX  | MEM | WB  |    |

|    |    |    |     | IF  | ID  | ΕX  | MEM | WB |

## 24. RISC Pipelining

# Chapter 15 sections 15.5

#### MIPS Instruction Set

- The MIPS instruction set was designed for pipeline execution

- MIPS instructions are the same length. x86 instructions vary from 1 byte to 17 bytes and pipelining is much more challenging.

- MIPS has only a few instruction formats, with the source operand being located in the same place in each instruction.

- Memory operands only appear in loads or stores in MIPS.

- Operands must be aligned in memory.

#### **MIPS** Instructions

- MIPS instructions classically take five steps:

- Instruction Fetch (IF)

- Instruction Decode & Register Fetch (ID)

- Execution / Effective Address (EX)

- Memory Access (MEM)

- Write Back Results (WO)

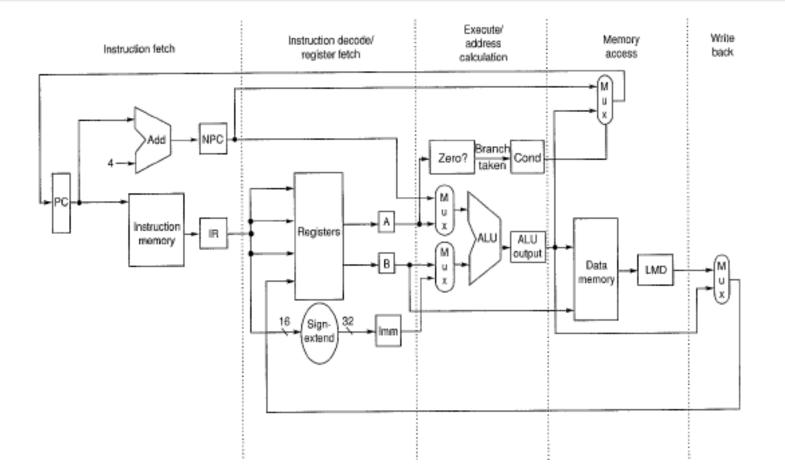

#### Non-pipelined RISC Processor (MIPS) 5 stages

## Instruction Fetch (IF)

- IF (Instruction Fetch)

IR <- M[PC]</li>

NPC <- PC + 4</li>

- IR: Instruction Register

- M: Memory

- PC: Program Counter

- NPC: Next Program Counter

- Fetch the instruction

- Update program counter

## Instruction Decode (ID)

- ID (Instruction Decode/Register Fetch)

- A <- Regs[rs]</li>

- B <- Regs[rt]

- Imm<- sign-extend immediate field of IR

- Decoding can be done in parallel with reading registers

- In an aggressive implementation the branch can be completed at the end of this stage as we will see later

## Execution (EX)

- Performs one of the following:

- Memory Reference

- ALUOutput <- A + immediate

- Register-Register ALU instruction

- ALUOutput<- A opcode B</li>

- Register-Immediate ALU instruction

- ALUOutput<- A opcode Imm

- Branch

- ALUOutput<- NPC + (Imm << 2)

- Cond <- (A==0)

### Memory Access (MEM)

- Memory Reference

- LMD <- Mem[ALUOutput] ; load from memory

- Mem[ALUOutput] <- B ; store to memory

- Branch

- if (cond) PC <- ALUOutput

## Write Back (WB)

- Register-Register ALU

- Regs[rd] <- ALUOutput

- Register-Immediate ALU

- Regs[rt] <- ALUOutput

- Load instruction

- Regs[rt] <- LMD

|                                            | \terminal.s                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _ 8 ×                                  |

|--------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <u>File Execute Configure Window H</u> elp |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

| Cycles                                     | Registers                                      | _ <b>_ _</b> ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Statistics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u> </u>                               |

|                                            | ■      - 000000000000000000000000000000000000  | P0      000000.00000000      P1        P1      000000.00000000      P2      000000.0000000        P3      000000.0000000      P3      000000.0000000        P4      000000.0000000      P3      000000.0000000        P5      000000.00000000      P3      000000.00000000        P6      000000.00000000      P3      000000.00000000        P10      000000.00000000      P12      000000.00000000        P14      000000.000000000      P14      000000.00000000        P14      000000.0000000000      P14      000000.00000000        P14      000000.0000000000      P14      000000.000000000000000000000000000000 | Execution<br>0 Cycles<br>0 Instructions<br>Stalls<br>0 RAW Stalls<br>0 WAW Stalls<br>0 WAW Stalls<br>0 WAW Stalls<br>0 Structurel Stalls<br>0 Branch Taken Stalls<br>0 Branch Misprediction Stalls<br>Code size<br>40 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|                                            |                                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

| Pipeline                                   |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u> </u>                               |

| BX<br>Malipier<br>MBM<br>FP Adder<br>DIV 0 | 0008      000000000000000000000000000000000000 | B: .word 8<br>C: .word 0<br>CR: .word32 0x10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D000      dcd40000      ld ±d,A(t0)        0004      dc050008      ld ±5,B(t0)        0006      0053182      dadd ±5,t4,t5        000c      tc035182      dadd ±5,t4,t5        000c      tc035182      dadd ±5,t4,t5        0001      tc010015      lwu ±1,CK(±0)        0018      tc030001      dadd ±10,t0,1        0016      tc030001      dadd ±10,t0,1        0021      tc240000      sd ±3,(t2)        0022      tc240000      sd ±3,(t2)        0021      tc240000      sd ±10,(t1)        0022      tc240000      sd ±10,(t1)        0024      tc200000      halt        0025      tc000000      tc33<0000000        0036      tc0000000      tc34        0040      tc000000      tc44        0040      tc000000      tc44        0040      tc000000      tc44        0040      tc4000000      tc44        0040      tc4000000      tc44        0040      tc4000000      tc44        0044      tc4000000 | Control F<br>Data Regi                 |

| IF ID HILD WE                              | 0008      000000000000000000000000000000000000 | B: .word 8<br>C: .word 0<br>CR: .word32 0x10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0004 dc050008      ld r5,B(t0)        0006 0055182c      dad r3,C(r0)        0016 0055182c      add r3,C(r0)        0010 dc01018      lwu r1,CR(r0)        0014 8c020020      lwu r2,DR(r0)        0016 fc030000      daddr1,10,c0,1        0016 fc030000      sd r3,(r1)        0024 0400000      sd r3,(r1)        0024 0400000      halt        0026 0000000      0036 0000000        0038 0000000      0038 0000000        0044 0000000      0044 0000000        0038 00000000      0044 0000000        0044 00000000      0040 0000000        0044 00000000      0040 0000000                                                                                                                                                                                                                                                                                                                               | ;Control F<br>;Data Regi<br>;r3 output |

## WINMIPS64

#### WinMIPS64

- WinMIPS64 is an instruction set simulator

- You can:

- Load MIPS programs

- Execute one cycle at a time

- Visualize the pipeline

- You can download the software and read the documentation here:

- <u>http://indigo.ie/~mscott/</u>

#### WinMIPS64 Example

- Open notepad, copy the following into a new notepad file, and save it as test.s

- Copy WinMIPS64 from the CS 430 public folder

- Open WinMIPS64

- From WinMIPS64, open test.s

- Step through the program using F7