# More Cache Schemes

Advantages of direct mapping:

- 1. The technique is simple

- 2. The mapping scheme is easy to implement

Disadvantage of direct mapping:

1. Each block of main memory maps to a fixed location in the cache; therefore, if two different blocks map to the same location in cache and they are continually referenced, the two blocks will be continually swapped in and out (known as thrashing).

## (2) Associative Mapping

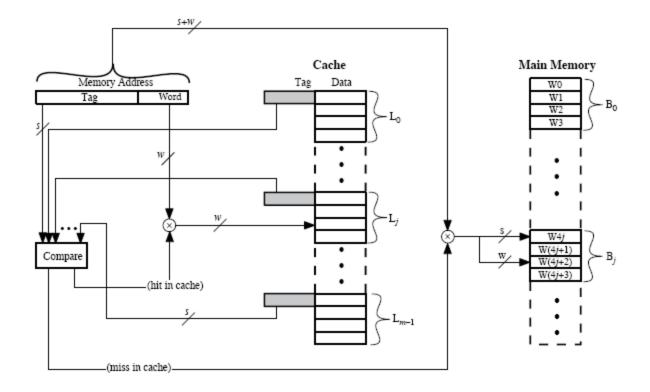

With associative mapping, any block of memory can be loaded into any line of the cache. In this case, a memory address is simply a tag and a word (note: there is no field for line #). To determine if a memory block is in the cache, each of the tags are simultaneously checked for a match.

To summarize:

Address Length is (s + w) bits

Number of addressable units is 2<sup>s+w</sup> bytes

Block size = line size =  $2^{W}$  bytes

Number of blocks in main memory is  $\frac{2^{s+w}}{2^w} = 2^s$

Number of cache lines is undetermined

Tag size is (s) bits

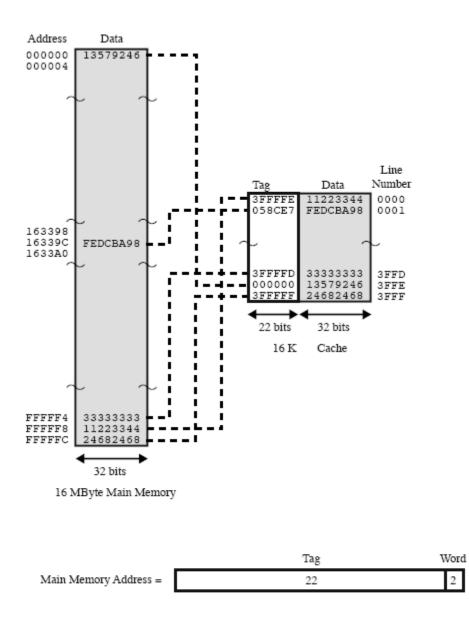

Let's go through the following example:

Figure 4.9 Fully Associative Cache Organization [HWAN93]

Figure 4.10 Associative Mapping Example

## Advantage of associative mapping:

1. There is flexibility when mapping a block to any line of the cache

## Disadvantages of associative mapping:

1. A replacement algorithm must be used to determine which line of cache to swap out

2. More space is needed for the tag field

3. The most important disadvantage is the complex circuitry needed to examine all of the tags in parallel in the cache

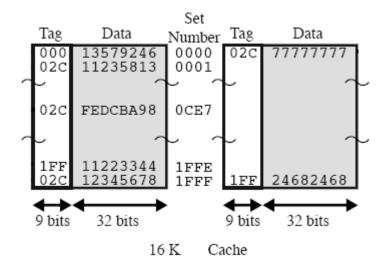

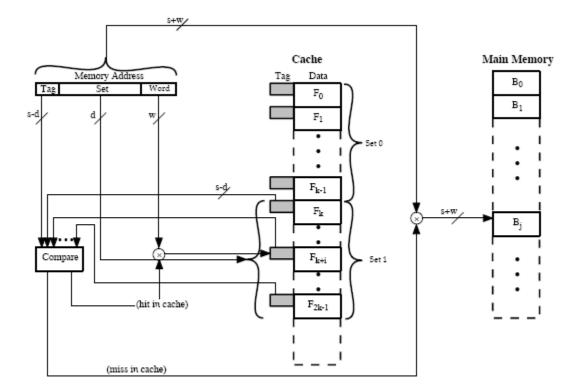

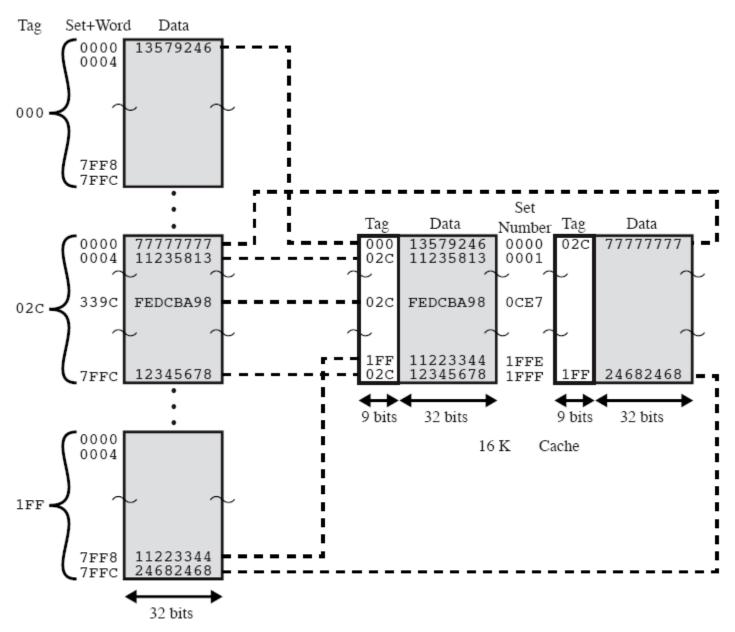

### 3) Set Associative Mapping

Set associative mapping utilizes the strengths of both direct and associative mapping while trying to reduce their disadvantages. With set associative, the cache is divided into v sets where each set consists of k lines.

Here is a two-way set associative cache that we will go into detail a little later.

The relationships are as follows:

m = v x ki = j module v

where

i = cache set number

j = main memory block number

m = number of lines in the cache

v = set number

k = number of lines in a set (two-way set associative means two lines per set)

To summarize:

Address Length is (s + w) bits

Number of addressable units is 2<sup>s+w</sup> bytes

Block size = line size =  $2^{w}$  bytes

Number of blocks in main memory is  $\frac{2^{s+w}}{2^{w}} = 2^{s}$

Number of lines in a set = k

Number of sets is  $v = 2^d$

Number of lines in the cache is  $kv = k \times 2^d$ Size of tag is (s - d) bits

Let's go through the following example:

Figure 4.11 k-Way Set Associative Cache Organization

16 MByte Main Memory

Reading for next time is pp. 123-131

Replacement Algorithms & Write Policies Multilevel caches Pentium 4 and PowerPC Cache Organizations 1. The following cache represents a 2-way set associative cache, i.e., there are two lines per set. Notice that the set ID values start at 01101101<sub>2</sub> and increment every other row. This is meant to imply that you are looking at a group of lines/sets toward the middle of the cache and not the entire cache. There are 14 bits for the tag, 8 bits for the set id, and 2 bits for the word id. Answer the following 3 questions based on this cache.

| Tag<br>(binary values) | Set ID<br>(binary<br>values) | Word within block |              |              |              |

|------------------------|------------------------------|-------------------|--------------|--------------|--------------|

|                        |                              | 00                | 01           | 10           | 11           |

| 10100001001001         | 01101101                     | 0016              | <b>61</b> 16 | C216         | 2316         |

| 11100001100100         | 01101101                     | <b>10</b> 16      | <b>71</b> 16 | D216         | 3316         |

| 11001011010110         | 01101110                     | 2016              | <b>81</b> 16 | E216         | 4316         |

| 11100101101011         | 01101110                     | 3016              | <b>91</b> 16 | F216         | 5316         |

| 11110110110100         | 01101111                     | 4016              | <b>A1</b> 16 | 0216         | 6316         |

| 10100111010101         | 01101111                     | 5016              | B116         | 1216         | 7316         |

| 10101010111110         | 01110000                     | 8416              | E516         | 4616         | A716         |

| 10101010010011         | 01110000                     | <b>94</b> 16      | F516         | 5616         | B716         |

| 01110001001000         | 01110001                     | A416              | A516         | <b>66</b> 16 | C716         |

| 00001101101101         | 01110001                     | B416              | 1516         | <b>76</b> 16 | D716         |

| 01011010010010         | 01110010                     | C416              | 2516         | 8616         | E716         |

| 10101111001011         | 01110010                     | D416              | 3516         | <b>96</b> 16 | <b>F7</b> 16 |

- 1. A copy of the data from memory address 7121C5 (hex) is contained in the portion of the cache shown above. Enter the value that was retrieved from that address in the space below as a two-digit hexadecimal number.

- 2. How many lines are contained in this cache?

- a. 8

- b. 256

- c. 512

- d. 1024

- e. 16K

- f. Cannot be determined

- 3. How many blocks are contained in the memory space?

- a. 2^24

- b. 2^22

- c. 2^14

- d. 2^8

- e. 2^2

- f. Cannot be determined

2. Suppose physical addresses are 32 bits wide. Suppose there is a cache containing 256K words of data (not including tag bits), and each cache block contains 4 words. For each of the following cache configurations,

- a. direct mapped

- b. 2-way set associative

- c. 4-way set associative

- d. fully associative

specify how the 32-bit address would be partitioned. For example, for a direct mapped cache, you would need to specify which bits are used to select the cache entry and which bits are used to compare against the tag stored in the cache entry.

3. The Magiccomputer Corporation manufacturers a machine with a cache that contains four lines. Main memory consists of 16 blocks.

Suppose a program starts out by referencing blocks 0, 3, 4, 9, and 5, in that order. After this series of references is made, which blocks are in the cache, and what are the tags (in binary) if the cache organization is Direct Mapping.

| Line | Тад | Block Number |

|------|-----|--------------|

| 0    |     |              |

| 1    |     |              |

| 2    |     |              |

| 3    |     |              |

After this series of references is made, which blocks are in the cache, and what are the tags (in binary) if the cache organization is 2-way set associative mapping.

| Line | Тад | Block Number |

|------|-----|--------------|

| 0    |     |              |

| 1    |     |              |

| 2    |     |              |

| 3    |     |              |