# CS430 Computer Architecture

# Spring 2015

CS430 - Computer Architecture

# More Pipelining

- Each instruction does not necessarily go through each stage of the pipeline

- 1. Give two different instructions where this is the case

- 2. The hope is that all of the stages can be performed in parallel. Give an example where this is not possible.

- 3. The conditional branch presents a particular problem. Why?

## **MIPS** Instructions

- MIPS instructions classically take five steps:

- 1. Instruction Fetch

- 2. Instruction Decode & Register Fetch

- 3. Execute Instruction & Address Calculation

- 4. Memory Access

- 5. Write Back Results

## **MIPS Instruction Set**

- The MIPS instruction set was designed for pipeline execution

- 1. MIPS instructions are the same length. x86 instructions vary from 1 byte to 17 bytes and pipelining is much more challenging.

- 2. MIPS has only a few instruction formats, with the source operand being located in the same place in each instruction.

- 3. Memory operands only appear in loads or stores in MIPS.

- 4. Operands must be aligned in memory.

# **Conditional Branch**

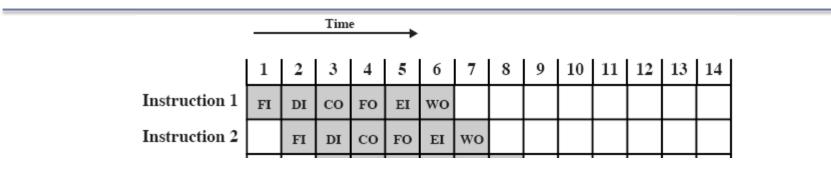

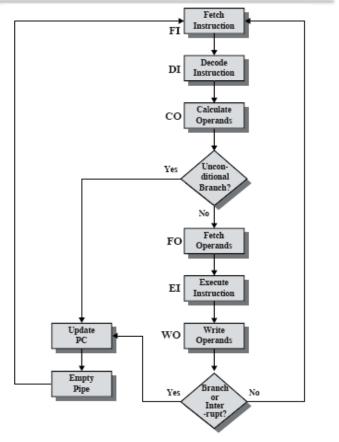

- Explain the following diagram

- which instruction is the branch

- what is the branch penalty

|                |    |    | Tim | e  | <b>→</b> |    |    |    |    |    |    |    |    |    |

|----------------|----|----|-----|----|----------|----|----|----|----|----|----|----|----|----|

|                | 1  | 2  | 3   | 4  | 5        | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |

| Instruction 1  | FI | DI | со  | FO | EI       | wo |    |    |    |    |    |    |    |    |

| Instruction 2  |    | FI | DI  | со | FO       | EI | wo |    |    |    |    |    |    |    |

| Instruction 3  |    |    | FI  | DI | со       | FO | EI | wo |    |    |    |    |    |    |

| Instruction 4  |    |    |     | FI | DI       | со | FO |    |    |    |    |    |    |    |

| Instruction 5  |    |    |     |    | FI       | DI | со |    |    |    |    |    |    |    |

| Instruction 6  |    |    |     |    |          | FI | DI |    |    |    |    |    |    |    |

| Instruction 7  |    |    |     |    |          |    | FI |    |    |    |    |    |    |    |

| Instruction 15 |    |    |     |    |          |    |    | FI | DI | со | FO | EI | wo |    |

| Instruction 16 |    |    |     |    |          |    |    |    | FI | DI | со | FO | EI | wo |

#### **Conditional Branch**

|      |     | FI | DI         | со    | FO    | EI    | wo |    |   |

|------|-----|----|------------|-------|-------|-------|----|----|---|

|      | 1   | 11 |            |       |       |       |    | 1  |   |

|      | 2   | 12 | 11         |       |       |       |    | 2  |   |

|      | 3   | в  | 12         | п     |       |       |    | 3  |   |

|      | 4   | 14 | 13         | 12    | n     |       |    | 4  |   |

|      | 5   | 15 | I4         | 13    | 12    | п     |    | 5  |   |

| 9    | б   | Ió | <b>I</b> 5 | 14    | 13    | 12    | п  | б  |   |

| Time | 7   | 17 | I6         | 15    | 14    | в     | 12 | 7  |   |

|      | 8   | 18 | 17         | 16    | 15    | I4    | в  | 8  |   |

|      | , 9 | 19 | I8         | 17    | 16    | 15    | I4 | 9  |   |

|      | 10  |    | 19         | 18    | 17    | I6    | 15 | 10 | I |

|      | 11  |    |            | 19    | 18    | 17    | Ió | 11 | ſ |

|      | 12  |    |            |       | 19    | I8    | 17 | 12 |   |

|      | 13  |    |            |       |       | 19    | I8 | 13 |   |

|      | 14  |    |            |       |       |       | 19 | 14 |   |

|      |     |    |            | (a) N | o bra | inche | 5  |    |   |

| FI<br>I1<br>I2<br>I3<br>I4<br>I5<br>I6<br>I7 | DI<br>11<br>12<br>13<br>14<br>15<br>16 | 11<br>12<br>13<br>14<br>15 | 11<br>12<br>13 | 11<br>12                              | wo                                       |

|----------------------------------------------|----------------------------------------|----------------------------|----------------|---------------------------------------|------------------------------------------|

| 12<br>13<br>14<br>15<br>16                   | 12<br>13<br>14<br>15                   | 12<br>13<br>14             | 12<br>13       | 12                                    | 11                                       |

| 13<br>14<br>15<br>16                         | 12<br>13<br>14<br>15                   | 12<br>13<br>14             | 12<br>13       | 12                                    | n                                        |

| 14<br>15<br>16                               | 13<br>14<br>15                         | 12<br>13<br>14             | 12<br>13       | 12                                    | n                                        |

| 15<br>16                                     | I4<br>I5                               | 13<br>14                   | 12<br>13       | 12                                    | n                                        |

| Ió                                           | 15                                     | I4                         | B              | 12                                    | п                                        |

| -                                            |                                        |                            |                |                                       | п                                        |

| I7                                           | Ić                                     | 15                         | 7.4            |                                       |                                          |

|                                              |                                        |                            | 14             | в                                     | 12                                       |

| 115                                          |                                        |                            |                |                                       | в                                        |

| 116                                          | 115                                    |                            |                |                                       |                                          |

|                                              | 116                                    | 115                        |                |                                       |                                          |

|                                              |                                        | I16                        | 115            |                                       |                                          |

|                                              |                                        |                            | I16            | 115                                   |                                          |

|                                              |                                        |                            |                | I16                                   | 115                                      |

|                                              |                                        |                            |                |                                       | 116                                      |

|                                              |                                        | 116                        | 116 115<br>116 | I16 I15   I16 I15   I16 I15   I16 I16 | 116 I15<br>116 I15<br>116 I15<br>116 I15 |

## **Conditional Branch**

• Any issues with the following diagram?

Figure 14.12. p. 499

## Question

- The CO stage might be delayed because the value used as part of the calculation depends on a register that will be effected by an instruction still in the pipeline.

- Give an example of this and show the pipeline as it would look when the problem is encountered.

## **Pipeline Hazards**

- 1. Give an example of each of the following hazards

- Structural hazards: Hardware cannot support the combination of instructions because the instructions need the same resource.

- Control hazards: Need to make a decision based on the results of one instruction while others are executing.

- Data hazards: An instruction depends on the results of a previous instruction still in the pipeline.

## **Pipeline Observations**

It is not necessarily the case that adding more stages to the pipeline increases performance because of the overhead involved with moving data along in the various buffers of the pipeline.

Increasing the number of stages increases the overhead of the control logic used to handle memory & register dependencies and in optimizing the pipeline.