#### Chapter 8 Main Memory

Images from Silberschatz

1

## How does the OS manage memory?

- Allocation

- Swapping

- Hardware support

- Pentium + Linux

- Assume the entire process must be in memory!

- Virtual Memory chapter 9

- Does not make this assumption

#### **Memory Access Basics**

- Register

- Cache

- Stall

- Main Memory

- Disk

- Protection

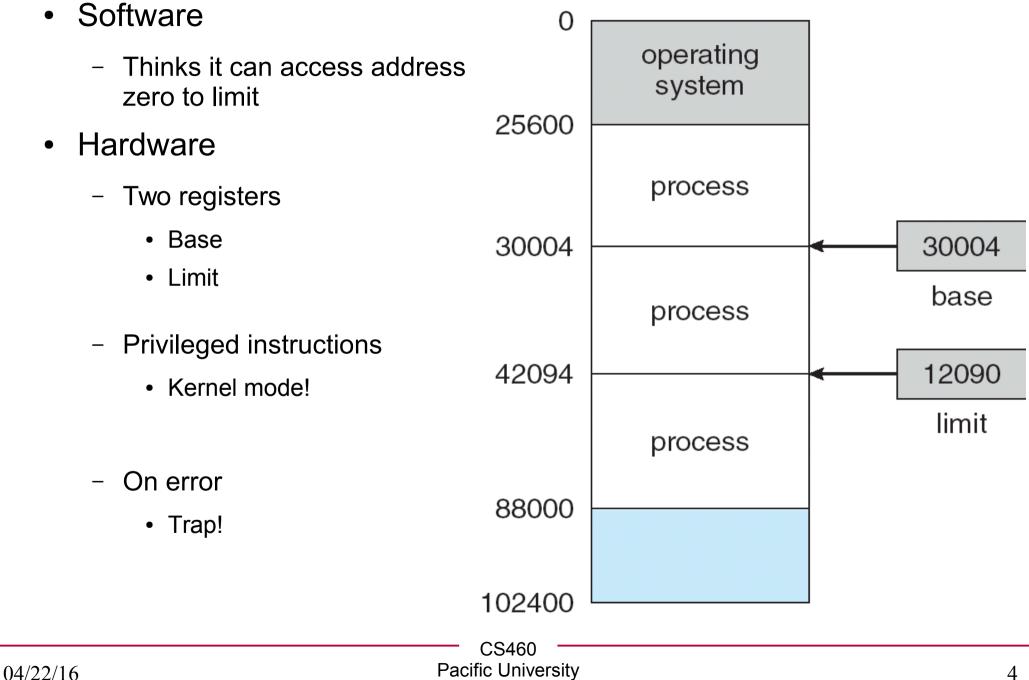

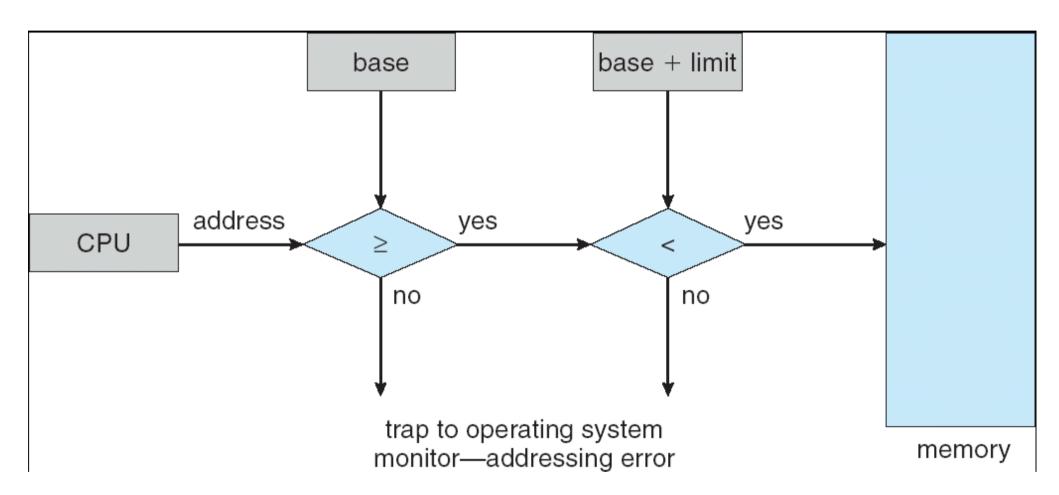

## (Basic) Mapping + Protection

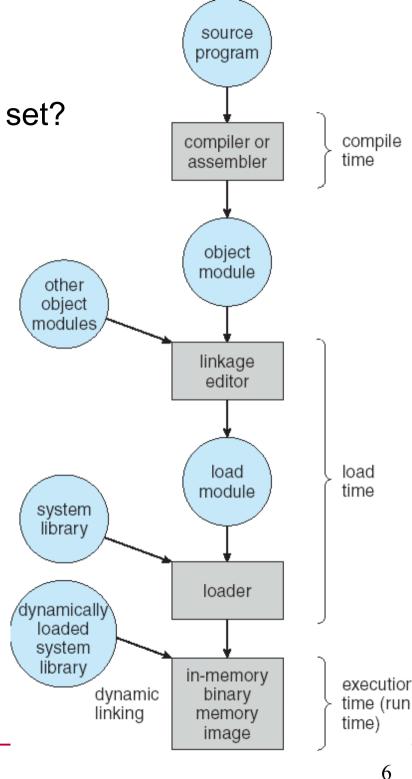

## Address Bind Time

- When are addresses in the executable set?

- Compile time

- Must always be in the same location

- Load time

- Can be loaded anywhere

- Execution time

- Can be moved during execution!

CS460 CS460 Pacific University

## Logical vs Physical Addresses

- Logical Address (Virtual Address)

- Software only ever sees this!

- register **Physical Address** 14000 • logical physical address address CPU memory +346 14346 Memory Management Unit ulletMMU Generalization of the base/limit register method

relocation

- Relocation register

## **Dynamic Linking**

- Linking at execution time

- Static linking

- stub

- Shared libraries

- .dll or .so

## Swapping

- Not all processes fit in physical memory

- Chapter 9: not all of a *single process* will fit into physical memory

- Physical memory <==> Backing store

- Swap back into memory

- Same location

- Different location

- Context Switch Time

- Size \* Transfer rate

- How does this affect time slices?

## **Contiguous Memory Allocation**

- Two Partitions

- OS

- User Processes

|          | CS460              |    |

|----------|--------------------|----|

|          |                    |    |

| 04/22/16 | Pacific University | 10 |

| 04/22/10 |                    | 10 |

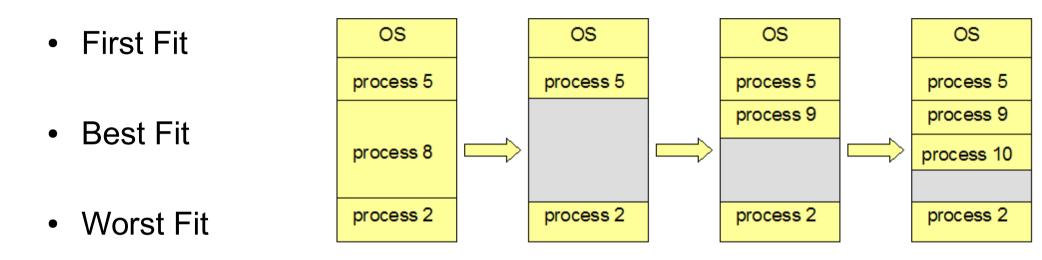

## Allocation of Memory

- Allocate part of User Space partition to each process

- Hole (technical term)

- Best Fit/First Fit found (experimentally) to be better than Worst Fit in terms of time and memory utilization

- What happens if 5 & 2 terminate?

#### Fragmentation

• External

• Internal

• Compaction

• 50% Rule

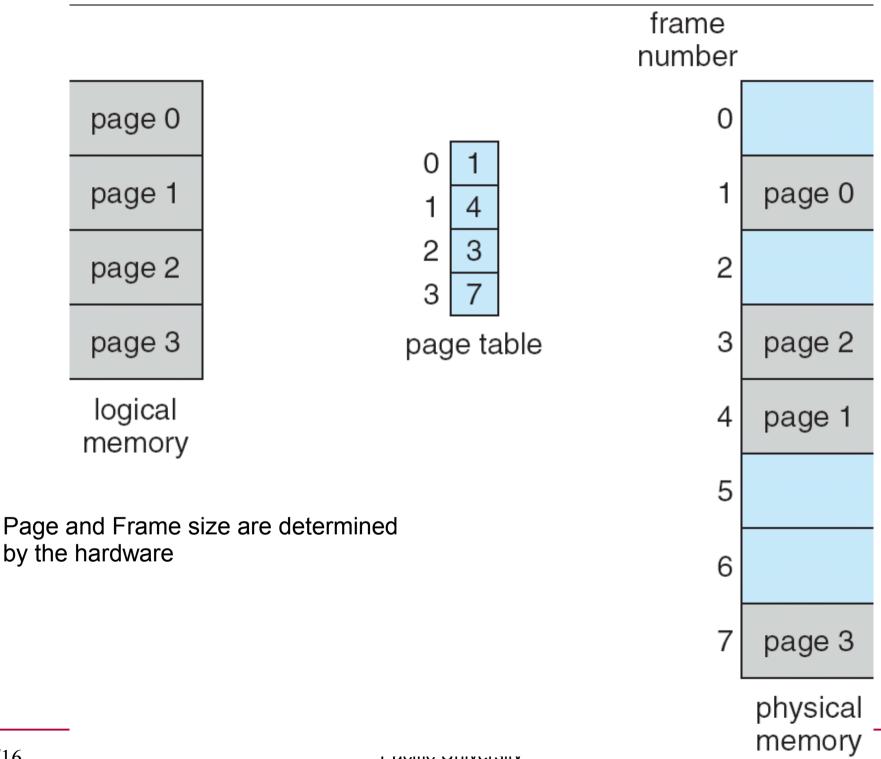

# Paging!

- Noncontiguous memory allocation

- Frame

- Physical memory

- Page

- Logical memory

- Allocate an entire page at a time

- Page table

- Internal Fragmentation

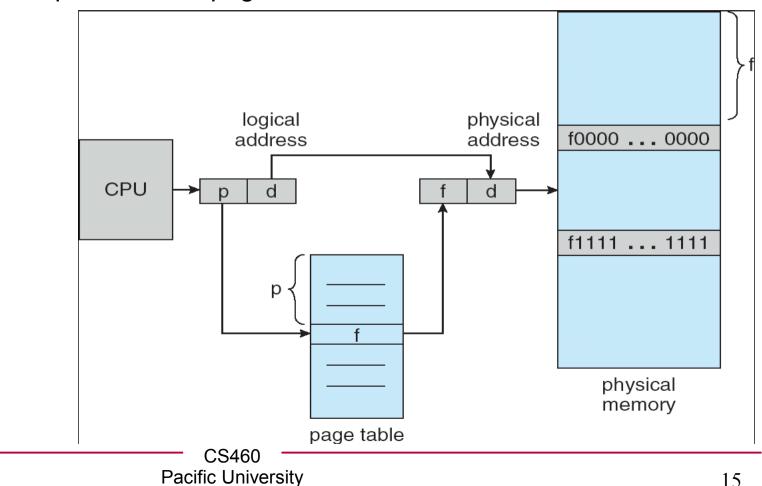

#### Address Translation

Logical Address to Page Number + Offset ullet

> page number page offset р d

> > n

*m* - *n*

Logical address space 2<sup>m</sup> and page size 2<sup>n</sup>

|                                                                | 0 a<br>1 b<br>2 c            |                          | 0        |                  |

|----------------------------------------------------------------|------------------------------|--------------------------|----------|------------------|

| 32 byte memory                                                 | 3 d<br>4 e<br>5 f<br>6 g     | 0 5                      | 4        | i<br>j<br>k      |

| <ul> <li>4 byte pages</li> </ul>                               | _7 h                         | 1 6                      |          | 1                |

| <ul> <li>No guarantee of<br/>ordering</li> </ul>               | 8 i<br>9 j<br>10 k<br>11 l   | 2 1<br>3 2<br>page table | 8        | m<br>n<br>o<br>p |

| <ul> <li>What happens</li> </ul>                               | 12 m<br>13 n<br>14 o<br>15 p |                          | 12       |                  |

| pChar ++;                                                      | logical memory               |                          | 16       |                  |

| <pre>print pChar;</pre>                                        |                              |                          | 20       | a<br>b<br>c<br>d |

|                                                                |                              |                          | 24       | e<br>f<br>g<br>h |

|                                                                |                              |                          | 28       |                  |

| 04/22/16                                                       | Pacific University           |                          | physical | memo<br>16       |

| $\mathbf{U} + (\mathbf{Z} \mathbf{Z} + \mathbf{I} \mathbf{U})$ |                              |                          |          | 10               |

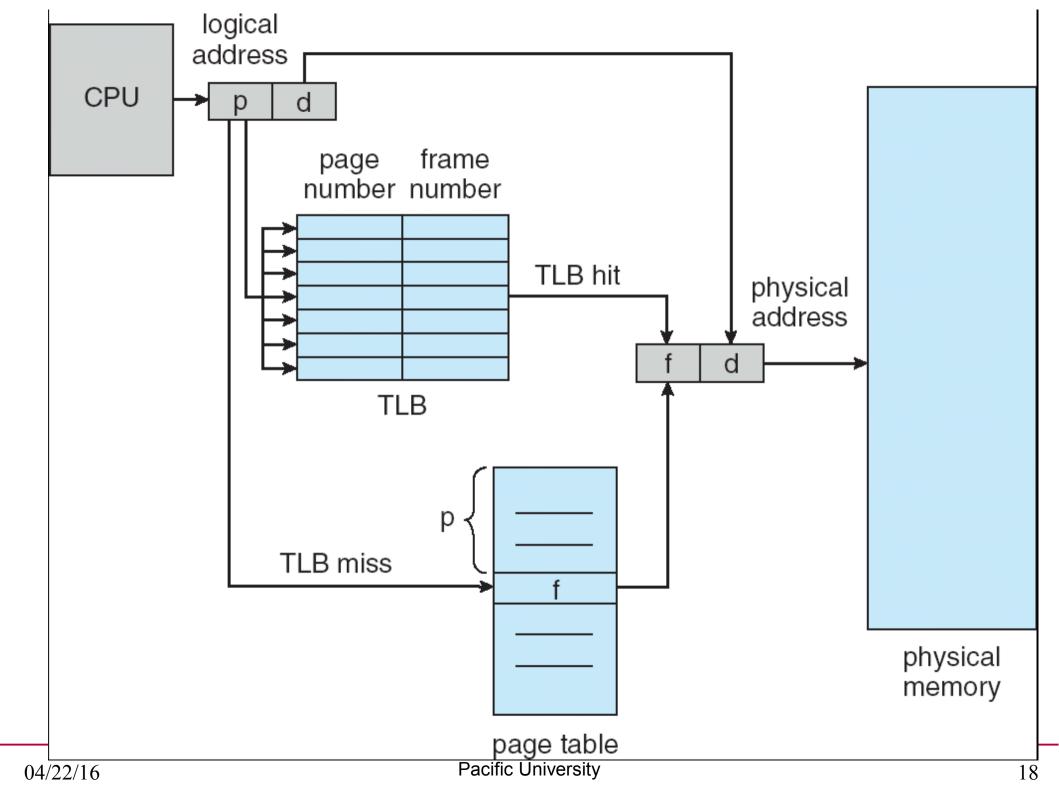

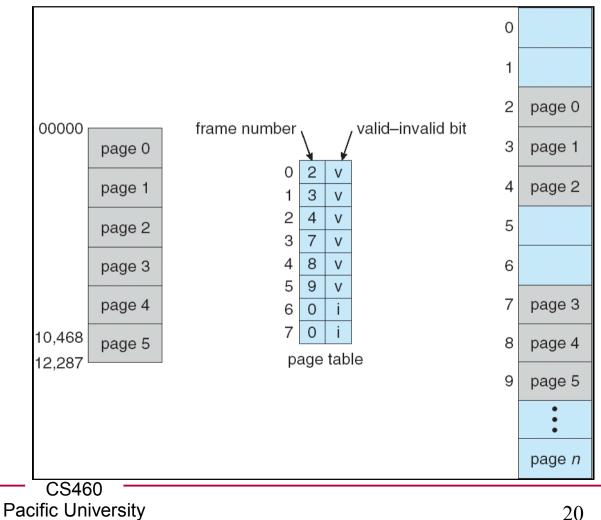

## Page Table

- Pages are not always reloaded to the same frame

- ??

- Contains base address of each page in physical memory

- Per process (usually)

- Which frame is it in

- In main memory

- Hardware (not per process)

- Page table base register (PTBR)

- Page table length register (PRLR)

- Translation look-aside buffers (TLBs)

- Address space identifiers (ASIDs)

- protection

### Logical -> Physical Address

- What do we need to do to get a physical address?

- How long will it take?

|          | CS460              |    |

|----------|--------------------|----|

| 04/22/16 | Pacific University | 19 |

#### Protection

• Add valid/invalid bit to each page table entry

• ASIDs in TLBs denote which process owns each frame

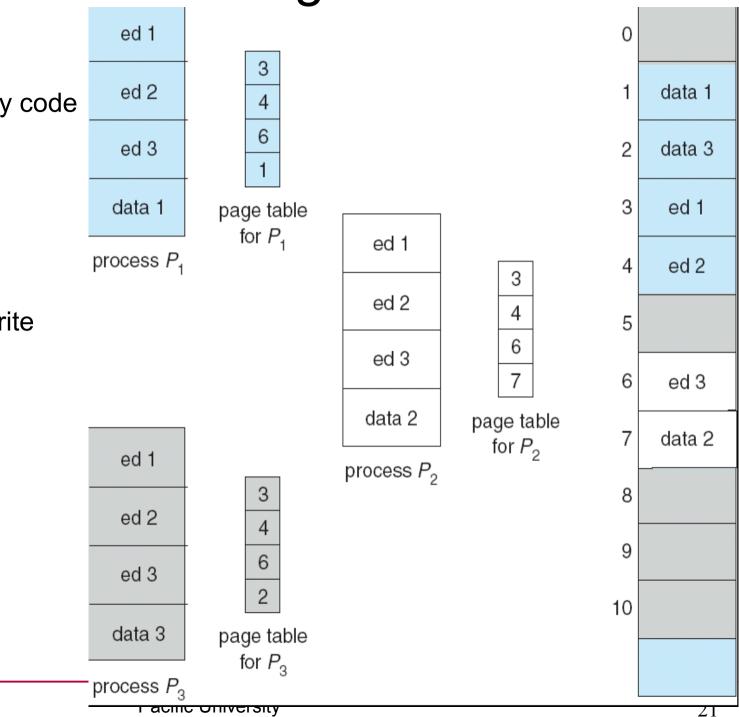

## **Shared Pages**

.dll / .so •

> - Share read only code pages

Shm •

> Shared read/write data pages

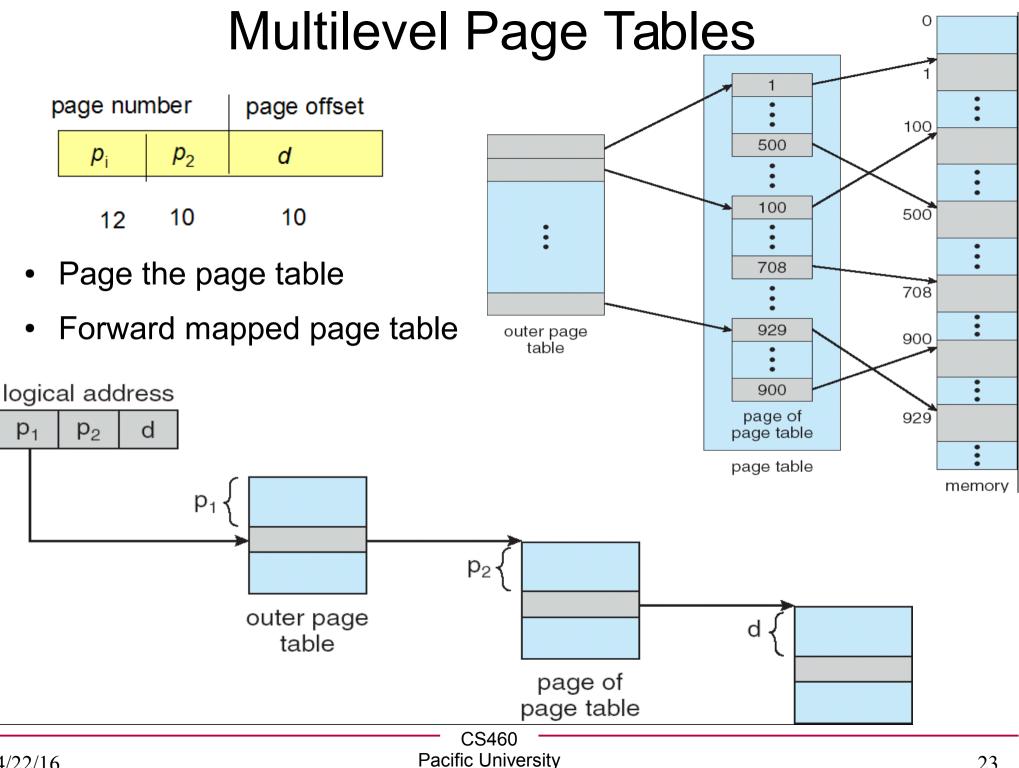

#### Problems with page tables

• What do you think?

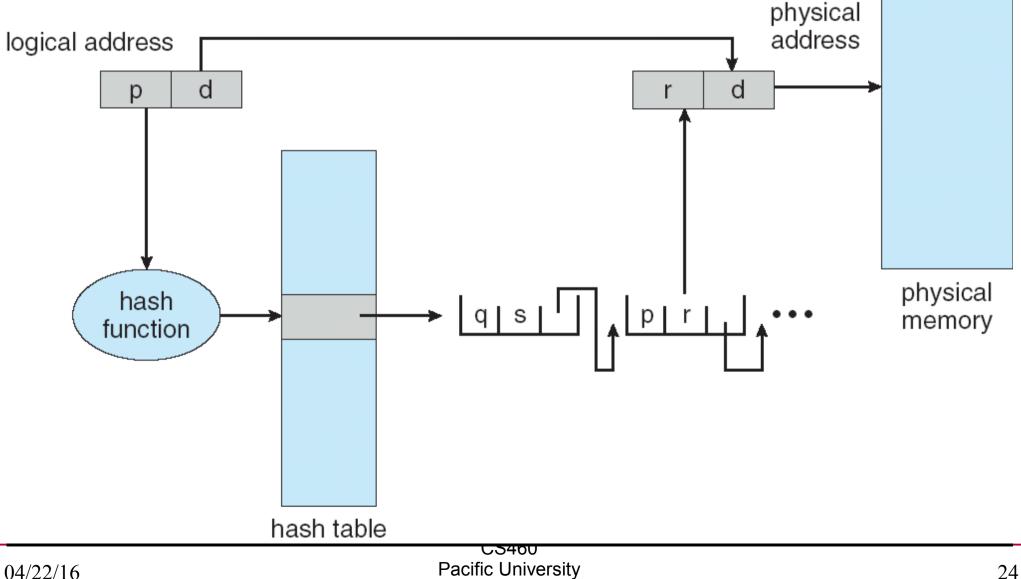

## Hashed Page Tables

- Address spaced > 32 bits

- Use Virtual address to hash into the table

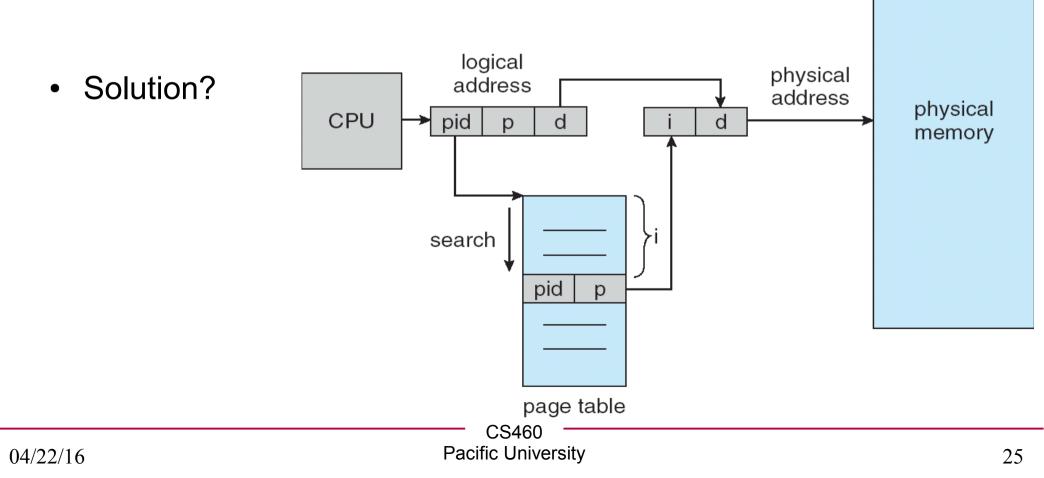

## Inverted Page Table

- One entry per *frame* in physical memory

- One page table for the entire system

- Track pid in the table

- Problem?